常用芯片相关概念

摘要

芯片相关的基础概念与区别。

基础单元

寄存器 register

顾名思义,寄存指将东西暂存在某处,请人代为保管。寄存器位于CPU内部,用来暂存数据或者CPU指令的一种物理结构。特点是速度快、容量小、成本相对内存和外存来说更高。CPU依赖寄存器来完成指令的读取和数据的保存。

缓存 cache

又称为高速缓存,用来给CPU核心或CPU cluster使用的弥补CPU寄存器和主存之间访问速度差异的物理结构。一般分为L1 cache(包括L1i cache和L1d cache)、L2 cache、L3 cache,速度依次递减,容量依次增大,成本依次递减。

1 | gh503@gh503-OMEN-by-HP-Laptop:~$ lscpu |

L1d caches: 一级数据缓存大小128KB,4个实例表示4个核心分别有128KBLi caches:一级指令缓存,同样4个核心分别128KBL2 caches:二级缓存,4个核心分别1MBL3 caches:三级缓存,4个核心公用6MB

主存 Memory

运行内存,程序运行时数据先加载到主存中,由CPU从主存中读取后执行。

RAM:Random-access Memory,随机访问存储器。MMU:Memory Management Unit,内存管理单元,内存控制器。PMMU:Paged Memory Management Unit,分页内存管理单元,内存控制器。

处理器和处理器核

- 处理器核:

CPU core,处理器内部最核心的部分,真正的处理器内核。 - 处理器:

CPU,中央处理器,也称通用处理器,计算机系统运算和控制核心,存储结构包括寄存器和缓存。

常用术语:

ALU:Arithmetic Logic Unit,算术逻辑单元,专门执行算术和逻辑运算的数字电路。Interrupt-Controller:中断控制器。PIC:Programmable IC,可编程中断控制器。GIC:Generic IC,通用中断控制器。VIC:Vectored IC,向量中断控制器。PLIC:Platform-level IC,RISC-V架构中断控制器。

微控制器 MCU

Micro-Controller Unit,俗称单片机。

比如常见的80C51系列单片机、Atmel公司的AVR系列单片机、ST公司的STM32系列单片机等,通过供电或极少的外围电路,烧写程序就可以工作。

微处理器 MPU

Micro-Processor Unit。微机中CPU被集成到一片超大规模集成电路上,可以说是广义CPU。比如STM32 Arm Cortex MPU。

狭义CPU和广义CPU

- 狭义

CPU:仅包括ALU和相应的控制电路,不包括IO控制器和控制器MMU。 - 广义

CPU:包括ALU和相应的控制电路,以及IO控制器、内存控制器、中断控制器,集成了大量外围控制器的单颗芯片。

目前市面上大都是广义CPU。

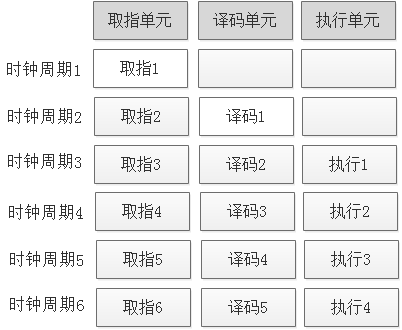

流水线 Pipeline

流水线,意指将产品生产过程划分成不同的工序进行生产的工艺。CPU中的流水线技术,通过分解CPU执行过程,然后逐个阶段完成执行。

通过足够细致的过程拆分,减少每个阶段的执行时间,并增加CPU核心的数量,来提高CPU的工作效率。

流水线技术存在短板效应,某个阶段的耗时过长会影响整个流水线的时长。

CPU需要靠内部的时钟驱动来工作,因为执行每条指令的时钟周期数量不变,所以可以通过降低时钟周期即提高时钟主频的方式来缩短每个阶段的执行时间。- 因为是分解后协同工作,可以通过增加

CPU核心数量的方式,让工作效率更高。

本质上,流水线技术是通过空间换时间,过程分解的越细,流水线越深,电路就越复杂,制造成本越大,功耗越大,工艺也越复杂。

参考文章:

[1]:深度解密 CPU 的缓存

[2]:深入浅出CPU流水线工作原理